SANTA CLARA, Calif. — An emerging 100-Gbit/s standard aims to create a lower-cost alternative to 2.5D chip stacks. Proponents believe that the ultra-short-reach interface could help to spawn an ecosystem for a growing set of system-in-package (SiP) designs.

The effort is one of many trying to craft 100G links in part so next-generation systems in data centers can handle the deluge of mobile and internet traffic. Engineers aim to make changes in chips, boards, and systems to enable 100G on copper, staving off for another generation a move to more expensive optical links.

The Common Electrical Interface 112G for multichip modules is one of the shortest of all of the efforts. Yet it could pave the way for a new class of high-end chips that don’t depend on Moore’s law for performance gains.

About 20 engineers from 14 companies, including Cisco Systems, Marvell, Microsoft, Microsemi, and Socionext, officially launched the effort last month. Startup Kandou Bus organized the group, hearing a need for a new class of multichip modules.

Many computer and comms chip vendors need to break up chips, which are getting increasingly large and difficult to yield. “Virtually everyone we talked to had this problem of needing to break up their chips; it was a chorus we heard,” said Brian Holden, director of product management at Kandou, who leads the standard at the Optical Internetworking Forum.

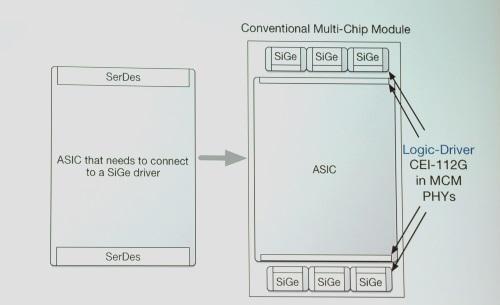

The effort, launched January 19th, proposes two links — a 1- to 10-Tbit link between two large logic chips and a 100G link between a large logic die and smaller driver chips. Both would run for less than a centimeter probably using two techniques, including Kandou’s interconnect that sends six bits over five wires.

The standard would enable multiple vendors to mix and match die on organic substrates in MCMs that could be made by any chip assembly vendor. It would provide an alternative to silicon interposers used in 2.5D chip stacks that are significantly more expensive due to yield, test, power, and thermal demands.

“People say that you have to bleed for a year to use a silicon interposer … but lots of people can make organic interposers — you don’t need exotic stuff,” said Holden in an interview on the DesignCon show floor.

To date, only relatively expensive, low-volume chips such as high-end FPGAs and some comms ASICs have used 2.5D stacks. The head of AMD’s GPU division recently complained that he wants to bring the 2.5D stacks to high-volume PC game applications, but they are still too costly.

Next page: Staving off the shift to optical links

The CEI-112G effort aims to enable new kinds of SiPs. (Image: OIF)

The CEI-112G effort aims to enable new kinds of SiPs. (Image: OIF)